|

|

| 中科院半导体研究所刘鸣团队:高效误码率监测方法研究 | MDPI Electronics |

|

论文标题:A Low-Cost Improved Method of Raw Bit Error Rate Estimation for NAND Flash Memory of High Storage Density

期刊:Electronics

作者: Kainan Ma,Ming Liu,Tao Li,Yibo Yin and Hongda Chen

发表时间:12 November 2020

DOI:10.3390/electronics9111900

微信链接:

https://mp.weixin.qq.com/s?__biz=MzI1MzEzNjgxMQ==&mid=2649991303&idx=2&sn=

fb635dc269edd859c7435ea00088bbd4&chksm=f1de1243c6a99b557362f49640c620e2

b09191fc3f68074004a4327c1239c3854c72ce310374&token=1684851637&lang=zh_CN#rd

期刊链接:https://www.mdpi.com/journal/electronics

通讯作者简介

刘鸣

中国科学院半导体研究所

刘鸣,副研究员,硕士生导师。2002年入清华大学微电子所,分别于2005年和2010年获硕士和博士学位;2010年入清华大学电子工程系博士后站,2012年8月出站后进入中国科学院半导体研究所工作至今。

主要研究领域包括于医疗电子、人工智能医学应用、低功耗数模混合SoC设计、多核处理器设计、数字低功耗设计方法、数字信号处理。

引言

大数据和5G时代的海量数据对存储设备的容量和速度提出了更高的需求,但固态硬盘SSD相较于机械硬盘 (HDD) 价格仍偏高,SSD中的NAND闪存需要在保持一定存储性能的前提下,进一步增加存储密度以降低成本。因此每单元能存储4 bit和5 bit 的QLC (quad-layer cell) 和PLC (Penta-Level Cell) 受到更多关注。然而存储密度的增加使NAND闪存中的数据更易受到噪声干扰而出错。因此有必要通过一种快速的误码率估计方法对高存储密度闪存的原始误码率 (RBER) 变化进行长期、频繁、及时的监测,以便主控能够及时选用合适的差错控制方法,保持闪存的性能和存储数据的安全。

近期,来自中国科学院半导体研究所的刘鸣研究员及其研究团队在Electronics期刊上发表了一篇论文,提出了一种可用在高存储密度闪存芯片上的快速、低成本的误码率监测方法,该方法具有很低的硬件复杂度,并且能够在一定程度上提升差错控制系统的纠错能力。

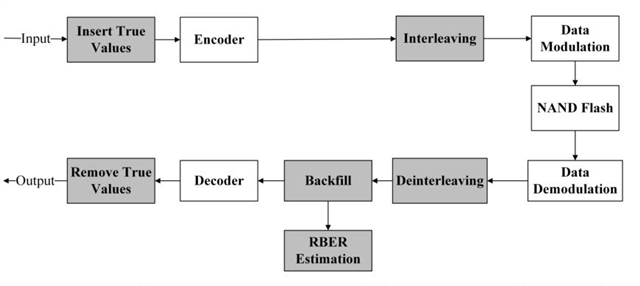

本论文提出了嵌入到NAND主控的差错控制系统中的RBER估计方法。其中灰色模块是关于提出的RBER估计方法的,白色模块是关于基于低密度奇偶校验码 (LDPC) 的差错控制过程的。

本论文贡献

本论文提出了一种嵌入在NAND闪存差错控制系统中的RBER估计方法,可以在读取数据的过程中完成RBER的统计和监测,不需要额外的时间,因而得到的结果能及时反映当前工作环境。该方法只需要采样少量的数据帧就能快速得到较准确的RBER。与传统的RBER估计方法相比,该方法平衡了高存储密度闪存单元上不均匀的页误码率分布,具有更广泛的适用性。同时本文利用估计时插入比较的真值和估计得到的RBER增强了差错控制系统的纠错能力,不仅弥补了由于RBER估计带来的速率降低,而且提高了NAND闪存的读取效率。

文章新颖性与设计亮点

本文采用了改进的真值插入比较方法估计NAND闪存的RBER,这种方法使用较少的数据帧就得到较准确的估计结果,因此可快速及时的得到RBER的变化情况。

交织器模块的引入使提出的RBER估计方法有更广泛的适用性。高存储密度NAND闪存的误码率分布受数据调制方法的影响可能会分布不均匀,并且不同NAND闪存设备采用的数据调制方法也不尽相同。这限制了真值插入比较法的适用范围和自适应性。本文引入的交织器模块消除了调制方法对误码率分布的影响,使所提出的RBER估计方法能适用于尽可能多的NAND闪存设备。

利用真值和估计得到的RBER提高了NAND闪存的读取效率。高存储密度的NAND闪存,如QLC、PLC,本身就面临读取速度慢的问题。为了不使RBER估计拖慢读取速度,本文从两个方面提高了读取效率。第一,通过估计得到的RBER支持译码状态的快速选择,缩短了读取时译码状态选择的时间;第二,基于真值和RBER改进了硬判决译码算法和软判决译码算法,增强了两者的纠错能力,减少了译码所需的迭代次数,缩短了译码时间。

测试结果

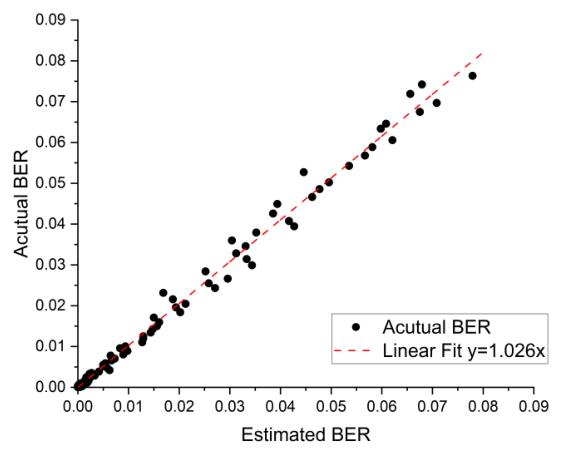

在插入占总数据长度3%的真值、采样16组数据帧的情况下,使用本文提出的估计方法得到的RBER与真实值的相关系数R2为0.992。因此可认为本文所提方法估计得到的RBER有较高的可信度。

估计的RBER与实际RBER的线性拟合,其中相关系数R2=0.992

当采用40 nm工艺库实现时,在最坏的工艺拐角条件下,在333 MHz的时钟速度下,所提出的RBER估计方法所需的模块总共只占用0.039 mm2,这对于NAND闪存的主控来说只增加了非常低的硬件成本。

在使用 (10080,8400) 的LDPC码测试时,当原始误码率接近该LDPC码纠错上界0.01时,改进后的译码算法需要平均25次迭代完成译码,而改进前的译码算法需要平均70次。后者在实际设备中会因为超出最大迭代次数被认定为译码失败,需要重新读取数据。这既会增加存储单元的磨损,又会增加读取延迟。当原始误码率为0.008时,改进的译码算法将迭代次数从18次降低到10次。这显示了本文改进的译码算法具有更强的纠错能力,从而提高了NAND闪存的读取效率。

小结

本文提出了一种适用于高存储密度NAND闪存的快速、及时、低成本的误码率估计方法,同时提出了一种利用插入的真值和估计得到的RBER增强硬判决译码算法和软判决译码算法的纠错性能的改进方法,提高了NAND闪存的读取效率。改进的译码算法加快了译码收敛速度,从而可以用更少的迭代来纠正错误。此外,它可以在最大迭代次数内纠正误码率接近差错控制编码上界的高误码率的数据帧,而不会陷入重读状态,从而降低读取延迟。提出的RBER估计方法的硬件复杂度非常低。因此,该方法对于需要长期、频繁地监测RBER变化的高存储密度NAND闪存具有很高的应用潜力。

Electronics(ISSN 2079-9292; IF:2.412) 是MDPI组织出版的国际性开放获取期刊之一,主题涵盖电子科学与应用领域,致力于发表电子器件、微电子与计算机技术、光电子工程、通信工程、信号与信息处理、微波理论与技术、生物电子工程、能源电子及系统等领域的各类文章。Electronics采取单盲同行评审,一审周期约为15.1天,文章从接收到发表仅需3.4天。

特别声明:本文转载仅仅是出于传播信息的需要,并不意味着代表本网站观点或证实其内容的真实性;如其他媒体、网站或个人从本网站转载使用,须保留本网站注明的“来源”,并自负版权等法律责任;作者如果不希望被转载或者联系转载稿费等事宜,请与我们接洽。